- 您现在的位置:买卖IC网 > Sheet目录287 > 24LC21-I/P (Microchip Technology)IC EEPROM 1KBIT 400KHZ 8DIP

�� �

�

�

�24LC21�

�3.1.4�

�DATA� VALID� (D)�

�3.1.5�

�ACKNOWLEDGE�

�The� state� of� the� data� line� represents� valid� data� when,�

�after� a� Start� condition,� the� data� line� is� stable� for� the�

�duration� of� the� high� period� of� the� clock� signal.�

�The� data� on� the� line� must� be� changed� during� the� low�

�Each� receiving� device,� when� addressed,� is� obliged� to�

�generate� an� acknowledge� after� the� reception� of� each�

�byte.� The� master� device� must� generate� an� extra� clock�

�pulse� which� is� associated� with� this� Acknowledge� bit.�

�period� of� the� clock� signal.� There� is� one� clock� pulse� per�

�Note:�

�The� 24LC21� does� not� generate� any�

�bit� of� data.�

�Each� data� transfer� is� initiated� with� a� Start� condition� and�

�terminated� with� a� Stop� condition.� The� number� of� the�

�data� bytes� transferred� between� the� Start� and� Stop�

�conditions� is� determined� by� the� master� device� and� is�

�theoretically� unlimited,� although� only� the� last� eight� will�

�be� stored� when� doing� a� write� operation.� When� an�

�overwrite� does� occur,� it� will� replace� data� in� a� first� in� first�

�out� fashion.�

�Acknowledge� bits� if� an� internal� program-�

�ming� cycle� is� in� progress.�

�The� device� that� acknowledges� has� to� pull� down� the�

�SDA� line� during� the� acknowledge� clock� pulse� in� such� a�

�way� that� the� SDA� line� is� stable� low� during� the� high�

�period� of� the� acknowledge� related� clock� pulse.� Of�

�course,� setup� and� hold� times� must� be� taken� into�

�account.� A� master� must� signal� an� end� of� data� to� the�

�slave� by� not� generating� an� Acknowledge� bit� on� the� last�

�byte� that� has� been� clocked� out� of� the� slave.� In� this�

�case,� the� slave� must� leave� the� data� line� high� to� enable�

�the� master� to� generate� the� Stop� condition.�

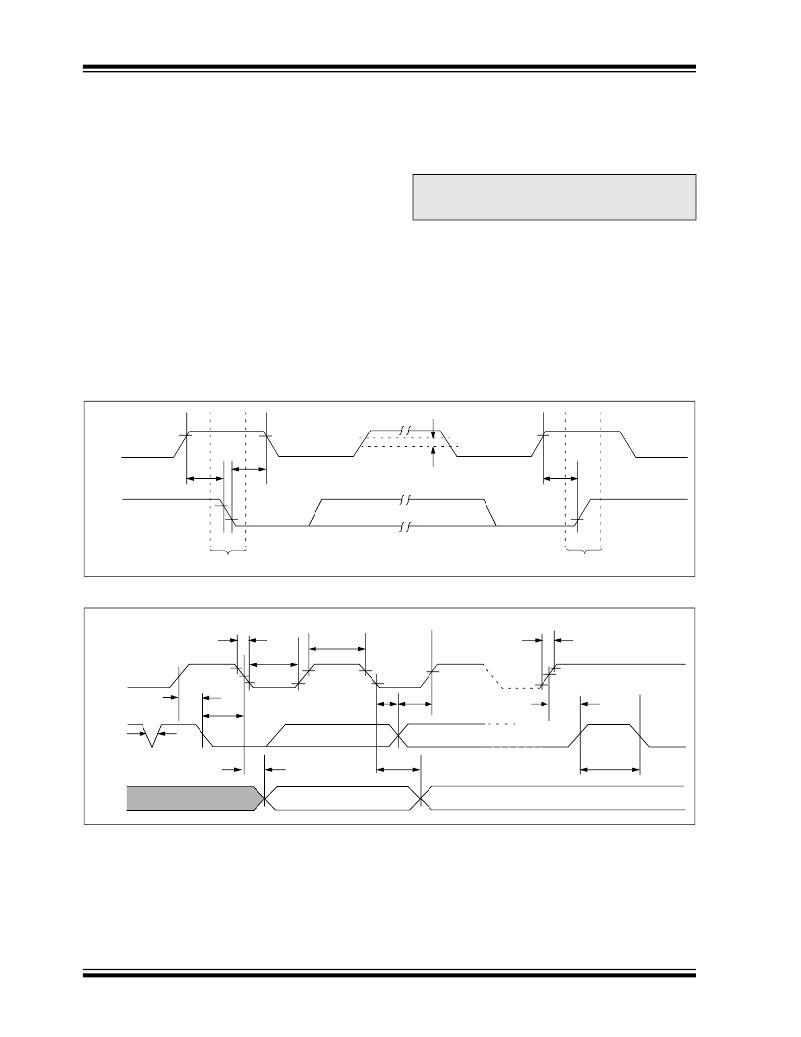

�FIGURE� 3-3:�

�BUS� TIMING� START/STOP�

�V� HYS�

�SCL�

�T� SU� :� STA�

�SDA�

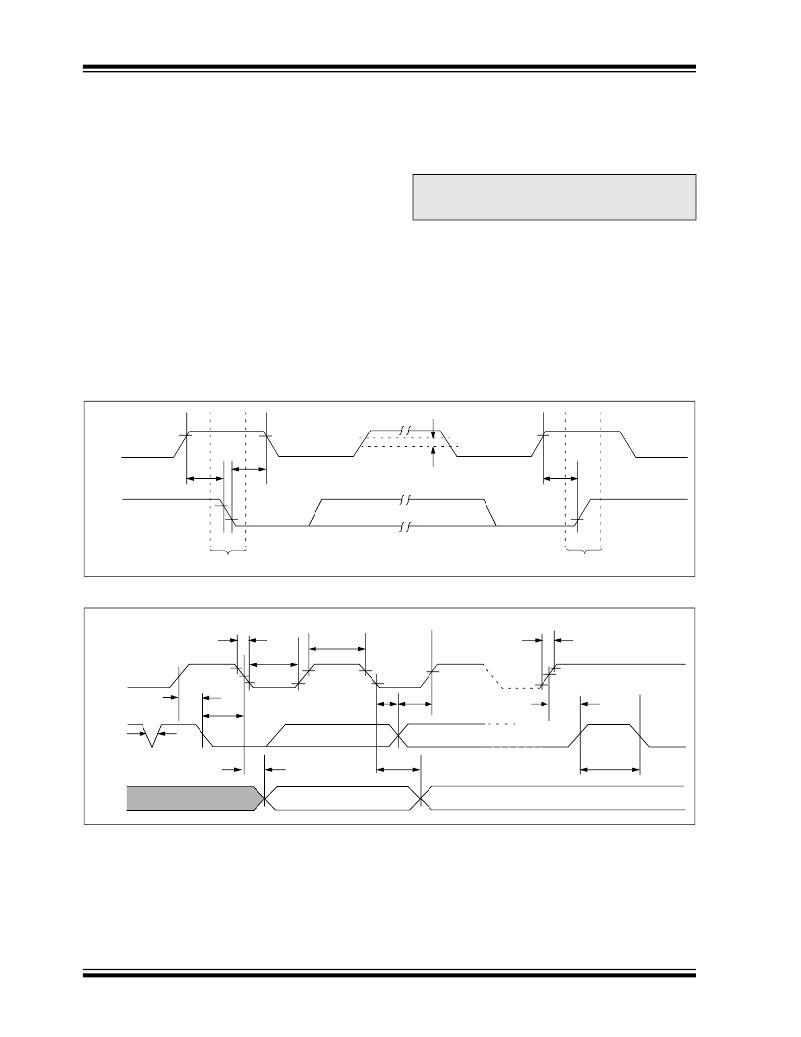

�FIGURE� 3-4:�

�T� HD� :� STA�

�Start�

�BUS� TIMING� DATA�

�T� F�

�T� LOW�

�T� HIGH�

�T� SU� :� STO�

�T� R�

�Stop�

�SCL�

�T� SU� :� STA�

�T� HD� :� DAT�

�T� SU� :� DAT�

�T� SU� :� STO�

�T� HD� :� STA�

�SDA�

�IN�

�T� SP�

�T� AA�

�T� HD� :� STA�

�T� AA�

�T� BUF�

�SDA�

�OUT�

�DS21095J-page� 6�

�?� 2004� Microchip� Technology� Inc.�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

24LC21A/P

IC EEPROM 1KBIT 400KHZ 8DIP

24LC22A-I/P

IC EEPROM 2KBIT 400KHZ 8DIP

24LC64XT-I/ST

IC SERIAL EEPROM 64K 2.5V 8TSSOP

24LCS21A/P

IC EEPROM 1KBIT 400KHZ 8DIP

24LCS22A-I/P

IC EEPROM 2KBIT 400KHZ 8DIP

24VL014/SN

IC EEPROM 1KBIT 400KHZ 8SOIC

24VL014H/SN

IC EEPROM 1KBIT 400KHZ 8SOIC

24VL024/SN

IC EEPROM 2KBIT 400KHZ 8SOIC

相关代理商/技术参数

24LC21-I/SN

功能描述:电可擦除可编程只读存储器 2.5V Dual Mode RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

24LC21T/SN

功能描述:电可擦除可编程只读存储器 2.5V Dual Mode RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

24LC21T-I/SN

功能描述:电可擦除可编程只读存储器 2.5V Dual Mode RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

24LC22A-I/P

功能描述:电可擦除可编程只读存储器 VESA E-EDID RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

24LC22A-I/PG

功能描述:电可擦除可编程只读存储器 VESA E-EDID Lead Free Package

RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

24LC22A-I/SN

功能描述:电可擦除可编程只读存储器 VESA E-EDID RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

24LC22A-I/SNG

功能描述:电可擦除可编程只读存储器 VESA E-EDID Lead Free Package

RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

24LC22AT-I/SN

功能描述:电可擦除可编程只读存储器 VESA E-EDID RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8